- 您现在的位置:买卖IC网 > Sheet目录1253 > XGBE-XGXS-O4-N2 (Lattice Semiconductor Corporation)IP CORE 10GBE ETHERNET XGXS

�� �

�

Lattice� Semiconductor�

�10Gb� Ethernet� XGXS� IP� Core� User’s� Guide�

�Management� Data� Input/Output� (MDIO)� Interface�

�The� MDIO� interface� provides� access� to� the� internal� XGXS� registers.� The� register� access� mechanism� corresponds�

�to� Clause� 45� of� IEEE� 802.3ae.� The� XGXS� core� provides� access� to� XGXS� registers� 0x0000-0x0024� as� speci� ?� ed� in�

�IEEE� 802.3ae.� Additional� registers� in� the� vendor-speci� ?� c� address� space� have� been� allocated� for� implementation-�

�speci� ?� c� control/status� functions.�

�The� physical� interface� consists� of� two� signals:� MDIO� to� transfer� data/address/control� to� and� from� the� device,� and�

�MDC,� a� clock� up� to� 2.5MHz� sourced� externally� to� provide� the� synchronization� for� MDIO.� The� ?� elds� of� the� MDIO�

�transfer� are� shown� in� Figure� 10.�

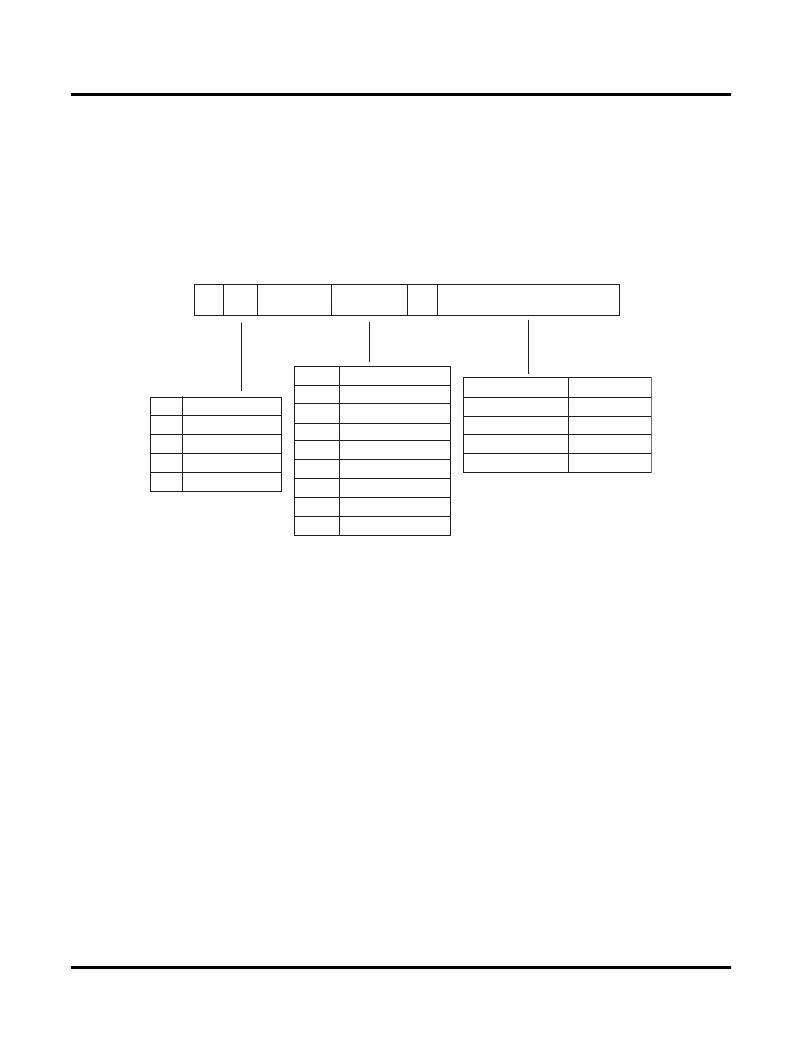

�Figure� 10.� Fields� of� MDIO� Protocol�

�ST�

�2b�

�OP�

�2b�

�PRTAD�

�5b�

�DTYPE*�

�5b�

�TA�

�2b�

�ADDRESS/DATA�

�16b�

�ST=00�

�VALUE�

�DEVICE� TYPE�

�0�

�RESERVED�

�ACCESS� TYPE�

�CONTENTS�

�OP�

�00�

�ACCESS� TYPE�

�ADDRESS�

�1�

�2�

�10G� PMA/PMD�

�10G� WIS�

�ADDRESS�

�WRITE�

�RESERVED�

�10G� PMA/PMD�

�01�

�WRITE�

�3�

�10G� PCS�

�READ� INCREMENT� 10G� WIS�

�10�

�11�

�READ� INCREMENT�

�READ�

�4�

�5�

�10G� PHY� XGXS�

�10G� DTE� XGXS�

�READ�

�10G� PCS�

�6-15�

�16-31�

�RESERVED�

�VENDOR� SPECIFIC�

�*� If� ST=01,� this� field� is� REGAD� (register� address).�

�Management� Frame� Structure�

�Each� management� data� frame� consists� of� 64� bits.� The� ?� rst� 32� bits� are� preamble� consisting� of� 32� contiguous� 1s� on�

�the� MDIO.� Following� the� preamble� is� the� start-of-frame� ?� eld� (ST)� which� is� a� 00� pattern.� The� next� ?� eld� is� the� opera-�

�tion� code� (OP)� that� is� shown� in� Figure� 10.�

�The� next� two� ?� elds� are� the� port� address� (PRTAD)� and� device� type� (DTYPE).� Since� the� physical� layer� function� in�

�10GbE� is� partitioned� into� various� logical� (and� possibly� separate� physical)� blocks,� two� ?� elds� are� used� to� access�

�these� blocks.� The� PRTAD� provides� the� overall� address� to� the� PHY� function.� The� ?� rst� port� address� bit� transmitted�

�and� received� is� the� MSB� of� the� address.� The� DTYPE� ?� eld� addresses� the� speci� ?� c� block� within� the� physical� layer�

�function.�

�Device� address� zero� is� reserved� to� ensure� that� there� is� not� a� long� sequence� of� zeros.� If� the� ST� ?� eld� is� 01� then� the�

�DTYPE� ?� eld� is� replaced� with� REGAD� (register� address� ?� eld� of� the� original� clause� 22� speci� ?� cation).� The� XGXS� core�

�does� not� respond� to� any� accesses� with� ST� =� 01.�

�The� TA� ?� eld� (Turn� Around)� is� a� 2-bit� turnaround� time� spacing� between� the� device� address� ?� eld� and� the� data� ?� eld� to�

�avoid� contention� during� a� read� transaction.� The� TA� bits� are� treated� as� don’t� cares� by� the� XGXS� core.�

�During� a� write� or� address� operation,� the� address/data� ?� eld� transports� 16� bits� of� write� data� or� register� address�

�depending� on� the� access� type.� The� register� is� automatically� incremented� after� a� read� increment.� The� address/data�

�?� eld� is� 16� bits.�

�For� an� address� cycle,� this� ?� eld� contains� the� address� of� the� register� to� be� accessed� on� the� next� cycle.� For�

�read/write/increment� cycles,� the� ?� eld� contains� the� data� for� the� register.� The� ?� rst� bit� of� data� transmitted� and� received�

�in� the� address/data� ?� eld� is� the� MSB� (bit� 15).� An� example� access� is� shown� in� Figure� 11.�

�16�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XM2D-0901

CONNECTOR

XM2D-3701

CONNECTOR

XM4M-2432-1312

CONN DVI 24POS 1.5A 40V DIGITAL

XM4M-2932-1311

CONN DVI 29POS 1.5A DIGTL/ANALOG

XM7B-0442

CONN USB 1A 30VAC R/A WHITE

XOCLCC6EVB

EVAL BOARD FOR XOCLCC6

XR16M890IL32-0C-EB

BOARD EVAL XR16M890IL32

XR18W750/753-0B-EB

EVAL BOARD FOR XR18W750/753

相关代理商/技术参数

XGC

制造商:Excelsys Technologies 功能描述:Power Suply, 36V@5.6A, Open Frame, Cage Mount, Modular, UltiMod Series 制造商:Excelsys Technologies 功能描述:MODULE POWER 28.8V-39.6V 5.6A

XGC10-88-S20

制造商:Johnson Electric / Saia-Burgess 功能描述:Catalogue / XGC10-88-S20 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC10-88-S20

XGC11-88-S20

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S20

XGC11-88-S20Z1

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S20Z1

XGC11-88-S40

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S40

XGC12-81Z1

制造商:Johnson Electric / Saia-Burgess 功能描述:Catalogue / XGC12-81Z1

XGC12-88

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC12-88

XGC12-88-J23

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC12-88-J23